Our assignment was to compare the performance and development workflows for other architectures

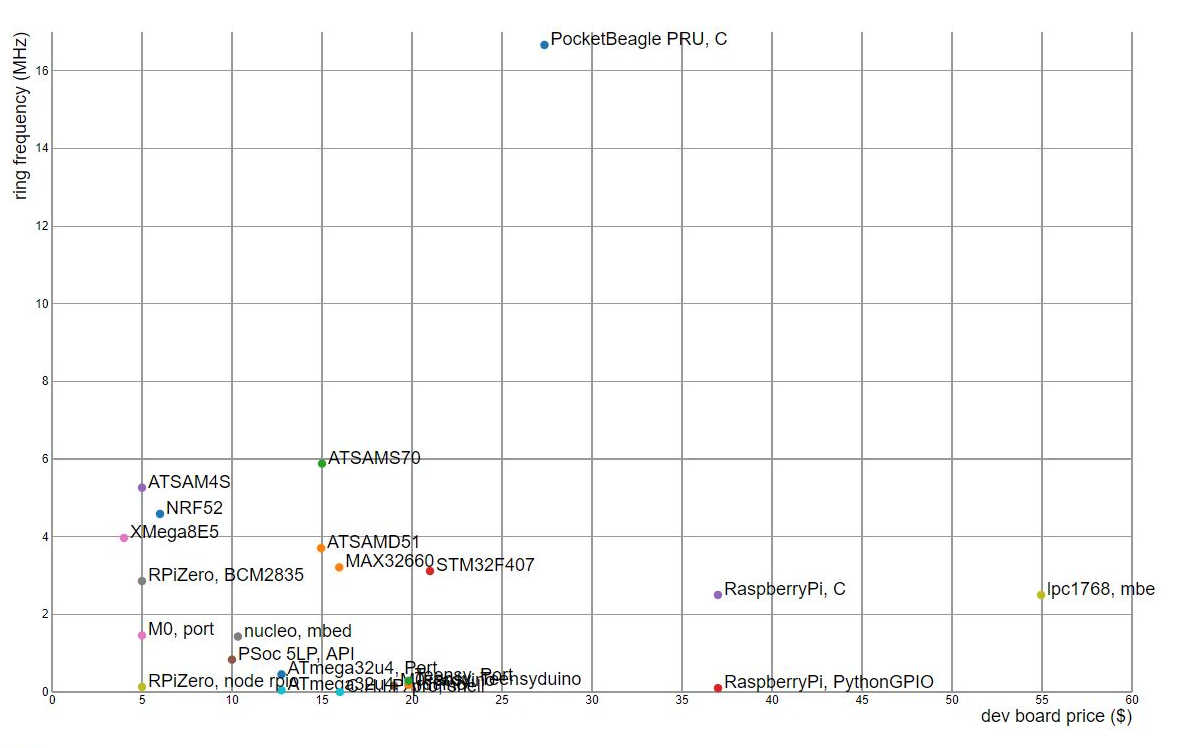

Here they define speed as how fast information can transit from external electronics into the core where microcode is running and back out again. A good way to test this is by constructing a ring oscillator, which simply sends token back and forth, producing a waveform that can be measured with an oscilloscope.

To measure speed across a GPIO layer, they use a logic level as the token. They also enforce that the token must reach the CPU, where code is running, rather than simply be inverted by digital logic or an event system.

To measure speed across a radio link, they use the smallest supported packet.

Here thry test embedded platforms that stray from the Harvard Architecture ... I.E FPGAs, PSOCs etc, including event systems or digital logic configurable in other microcontrollers (i.e. the XMEGA).

Source-

https://pub.pages.cba.mit.edu/ring/

Figure shows a configuration diagram of a typical embedded system consisting of two main parts: embedded hardware and embedded software. The embedded hardware primarily includes the processor, memory, bus, peripheral devices, I/O ports, and various controllers. The embedded software usually contains the embedded operating system and various applications.

Input and output are characteristics of any open system, and the embedded system is no exception. In the embedded system, the hardware and software often collaborate to deal with various input signals from the outside and output the processing results through some form. The input signal may be an ergonomic device (such as a keyboard, mouse, or touch screen) or the output of a sensor circuit in another embedded system. The output may be in the form of sound, light, electricity, or another analog signal, or a record or file for a database.

The basic computer system components—microprocessor, memory, and input and output modules—are interconnected by a system bus in order for all the parts to communicate and execute a program

In embedded systems, the microprocessor's role and function are usually the same as those of the CPU in a general-purpose computer: control computer operation, execute instructions, and process data. In many cases, the microprocessor in an embedded system is also called the CPU. Memory is used to store instructions and data. I/O modules are responsible for the data exchange between the processor, memory, and external devices. External devices include secondary storage devices (such as flash and hard disk), communications equipment, and terminal equipment. The system bus provides data

and controls signal communication and transmission for the processor, memory, and I/O modules.

There are basically two types of architecture that apply to embedded systems:

Von Neumann architecture and Harvard architecture.

Von Neumann architecture (also known as Princeton architecture) was first proposed by John von Neumann. The most important feature of this architecture is that the software and data use the same memory: that is,

“The program is data, and the data is the program”

In the Von Neumann architecture, an instruction and data share the same bus. In this architecture, the transmission of information becomes the bottleneck of computer performance and affects the speed of data processing; so, it is often called the Von Neumann bottleneck. In reality, cache and branch-prediction technology can effectively solve this issue.

The Harvard architecture was first named after the Harvard Mark I computer. Compared with the Von Neumann architecture, a Harvard architecture processor has two outstanding features. First, instructions and data are stored in two separate memory modules; instructions and data do not coexist in the same module. Second, two independent buses are used as dedicated communication paths between the CPU and memory; there is no connection between the two buses.

Because the Harvard architecture has separate program memory and data memory, it can provide greater data-memory bandwidth, making it the ideal choice for digital signal processing. Most systems designed for digital signal processing (DSP) adopt the Harvard architecture. The Von Neumann architecture features simple hardware design and flexible program and data storage and is usually the one chosen for general-purpose and most embedded systems.

To efficiently perform memory reads/writes, the processor is not directly connected to the main memory, but to the cache. Commonly, the only difference between the Harvard architecture and the Von Neumann architecture is single or dual L1 cache. In the Harvard architecture, the L1 cache is often divided into an instruction cache (I cache) and a data cache (D cache), but the Von Neumann architecture has a single cache.

The microprocessor is the core in embedded systems. By installing a microprocessor into a special circuit board and adding the necessary peripheral circuits and expansion circuits, a practical embedded system can be created. The microprocessor architecture

determines the instructions, supporting peripheral circuits, and expansion circuits. There are a wide range of microprocessors: 4-, 8-, 16-, 32-, and 64-bit, with performance from MHz to GHz, and ranging from a few pins to thousands of pins.

In general, there are two types of embedded microprocessor architecture:

reduced

instruction set computer (RISC) and complex instruction set computer (CISC).

The RISC processor uses a small, limited, simple instruction set. Each instruction uses a standard word length and has a short execution time, which facilitates the optimization of the instruction pipeline. To compensate for the command functions, the CPU is often equipped with a large number of general-purpose registers. The CISC processor features a powerful instruction set and different instruction lengths, which facilitates the pipelined execution of instructions.

| Comparison Parameter | RISC | CISC |

|---|---|---|

| Instruction System | Simple and efficient instructions | Rich instructions set |

| Memory Operation | Restricts Memory Operations and simplifies controlling functions | Has multiple memory operation instructions and performs direct operation |

| Program | Requires large amount of memory spaxe for the assembler | Has relatively simpler assembler features |

| Interruption | Responds to interrupts only at proper place of instruction execution | Responds to interruption only at the end of execution |

| CPU | Features fewer circuits, small size and low poer consumption | Featchers rich circuit and high power consumption |

| Design Cycle | Simple circuit and a compact layout, a short design cycle and easy application of new technologies |

Features complex structure and long design cycles |

| Usage | Simple control easya nd learning application | Complex strcuture powerful function, easy realization of special functions |

| Application Scope | Determines the instruction system per specific areas, which is more suitable for specific machines | Becomes more suitable for general purpose machines |

RISC and CISC have distinct characteristics and advantages, but the boundaries between RISC and CISC begin to blur in the microprocessor sector. Many traditional CISCs absorb RISC advantages and use a RISC-like design. Intel x86 processors are typical of them. They are considered CISC architecture. These processors translate x86 instructions into RISC-like instructions through a decoder and comply with the RISC design and operation to obtain the benefits of RISC architecture and improve internal operation efficiency. A processor's internal instruction execution is called micro operation, which is denoted as micro-OP and abbreviated mu-op (or written m-op or mop). In contrast, the x86 instruction is called macro operation or macro-op.

The entire mechanism is shown

Normally, a macro operation can be decoded into one or more micro operations to execute, but sometimes a decoder can combine several macro operations to generate a micro operation to execute. This process is known as x86 instruction fusion (macro-ops fusion). For example, the processor can combine the x86 CMP (Compare) instruction and the x86 JMP (Jump) instruction to produce a single micro operation—the compare and jump instruction. This combination has obvious benefits: there are fewer instructions, which indirectly enhances the performance of the processor execution. And the fusion enables the processor to maximize the parallelism between the instructions and consequently improve the implementation efficiency of the processor.

Currently, microprocessors used in most embedded systems have five architectures: RISC, CISC, MIPS, PowerPC, and SuperH.

Microprocessor without Interlocked Piped Stages (MIPS) is also a RISC processor. Its mechanism is to make full use of the software to avoid data issues in the pipeline. It was first developed by a research team led by Professor John Hennessy of Stanford University in the early 1980s and later was commercialized by MIPS Technologies. Like ARM, MIPS Technologies provides MIPS microprocessor cores to semiconductor companies through intelligence property (IP) cores and allows them to further develop embedded microprocessors in the RISC architecture. The core technology is a multiple-issue capability: split the idle processing units in the processor to virtualize as another core and improve the utilization of processing units. PowerPC Architecture PowerPC is a CPU in the RISC architecture. It derives from the POWER architecture, and its basic design comes from the IBM PowerPC 601 microprocessor Performance Optimized with Enhanced RISC (POWER). In the 1990s, IBM, Apple, and Motorola successfully developed the PowerPC chip and created a PowerPC-based multiprocessor computer. The PowerPC architecture features scalability, convenience, flexibility, and openness: it defines an instruction set architecture (ISA), allows anyone to design and manufacture PowerPC-compatible processors, and freely uses the source code of software modules developed for PowerPC. PowerPC has a broad range of applications from mobile phones to game consoles, with wide application in the communications and networking sectors such as switches, routers, and so on. The Apple Mac series used PowerPC processors for a decade until Apple switched to the x86 architecture.

Source- link

The ATmega328/P is a low-power CMOS 8-bit microcontroller based on the AVR® enhanced RISC (reduced instruction set computer) architecture. In Order to maximize performance and parallelism, the AVR uses Harvard architecture – with separate memories and buses for program and data. Instruction in the program memory are executed with a single level of pipelining. The clock is controlled by an external 16MHz Crystal Oscillator.

1.Automatic (Software) Reset: Rather then requiring a physical press of the reset button before an upload, the Arduino is designed in a way that allows it to be reset by software running on a connected computer. The Arduino Software (IDE) uses this capability to allow you to upload code by simply pressing the upload button in the Arduino environment. This means that the bootloader can have a shorter timeout, as the lowering of DTR (Data Terminal Ready) can be well-coordinated with the start of the upload.

2.Firmware: Firmware is a software program or set of instructions programmed on a hardware device. It provides the necessary instructions for how the device communicates with the other computer hardware. Firmware is held in non-volatile memory devices such as ROM.

3.To check whether the firmware is installed in your Arduino or not just press the reset button and if the inbuilt LED flickers (on pin 13) the firmware is present.

Source- link

"In electronics engineering and computer engineering, computer architecture is a set of disciplines that describes a computer system by specifying its parts and their relations." That's what wikipedia says. We'll, now what the computer actually is? To put it in simple words, its an assembly of different electronic (and some electrical) components, which manipulate electricity, in terms of electrical signals, to carry out computations. The arrangement and connection of these components, so that the signals propagate in the desired mannered for a given set of conditions in order to carry out a well defined operation, is computer architecture.